产品

FIB-SEM

Nanomanipulators

OmniProbeOmniProbe Cryo软件

AZtec3DAZtecFeatureAZtec LayerProbeTEM

Hardware

EDSUltim MaxXploreImaging

软件

AZtecTEM

自1947年巴丁和布拉顿在贝尔实验室发明了锗点接触晶体管以来,半导体已经深深融入人们的日常生活,从手机、汽车到大数据、物联网无一不依赖于半导体器件。存储芯片是半导体产业的重要分支,约占全球半导体市场的三分之一。根据IC Insights在2021年4月份的《麦克莱恩报告——集成电路行业的全面分析和预测》显示,在经历了2019年的大幅下跌后,内存集成电路的销售额在疫情困扰下的2020年反弹了15%,且预计会在2022和2023持续增长[1]。

在存储器中,DRAM(动态随机存储器,Dynamic RAM)和NAND Flash占了整个存储器市场份额的95%以上[2]。5G、人工智能等新兴产业的兴起对存储器的存储密度及读写速度、可靠性等都提出了更高的要求,DRAM已经实现1xnm制程量产且已开发出1znm工艺,NAND Flash开始从2D转向3D发展,旨在通过增加芯片的堆叠层数来获得更大的存储容量,如长江存储于2020年4月推出的128层堆栈的3D闪存。为了控制良率、分析失效机制及进一步提高性能,产业界和学术界都对存储器的表征投入了大量的精力,结构表征是其中必不可少的一环,本文将介绍牛津仪器纳米分析手段包括能谱 (EDS)、EBSD及纳米机械手Omniprobe在主流的半导体存储器中的应用。

1. SRAM

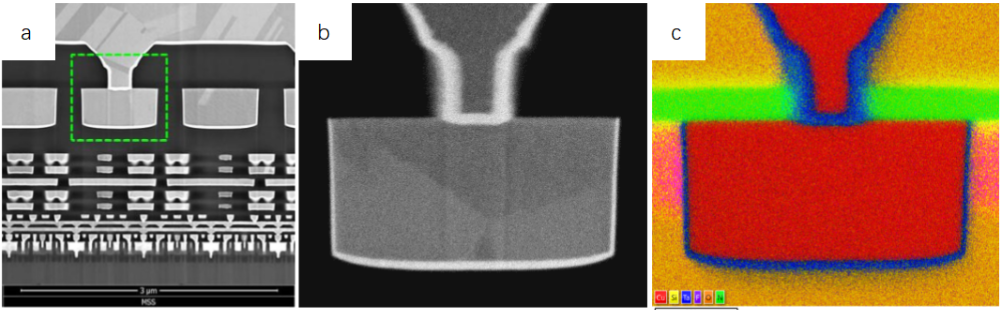

静态随机存取存储器(Static Random-Access Memory,SRAM)是随机存取存储器的一种,置于CPU与主存(DRAM)间的高速缓存,利用晶体管进行数据存储。图1所示为Samsung S8 SRAM上的金属连接部分的扫描电镜(SEM)图片及EDS元素分布图,EDS分析在2kV下完成。

先进制程中的金属连线通常使用Cu,为了防止Cu的扩散及改善Cu的附着能力等,需要在Cu导线与介质层间沉积Ta和TaN的复合层,金属层需用FSG或PSG进行隔绝。为了防止介质层在工艺过程中受损或者在环境中吸潮而影响性能,需要在介质层上镀介质势垒层进行保护,通常使用Si3N4。图1所示为大马士革镶嵌工艺制作的M11与M12间的连接。金属层周围的阻挡层TaN厚度在10nm尺度,图1(c)中蓝色即代表了区域内TaN的分布,与图1(b)中的电子图像完美匹配。金属层以上的势垒层Si3N4清晰可见,如图1(c)中的绿色区域,同时,F的分布(紫色)表明工艺中使用了低K介质材料来有效降低互联线的延迟时间。对比图1(b)可发现,在正常的二次电子像下,很难观察到势垒层和掺杂F的介质层分布,这也是元素分析在半导体应用中必不可少的原因之一。

2. DRAM

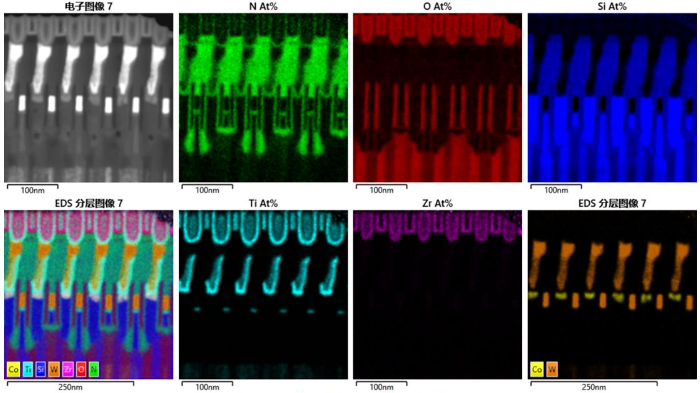

动态随机存取存储器(Dynamic Random Access Memory,DRAM)是一种易失性存储器,具有1T1C(一个晶体管一个电容)的结构,容量较SRAM大,速度介于SRAM和外部存储器间,因此用来加载程序与数据以供CPU直接运行与运用。DRAM的制作工艺不同于SRAM以及其它逻辑部件,3xnm存储器单元以后开始普遍采用鳍式晶体管和多层堆叠电容(ZAZ-TIT)[3]。多层堆叠电容中,每层结构厚度仅几纳米或更薄,制作电容介质层时需要使用ALD来进行原子层沉积。图2所示为一DRAM的字线(WL)和顶部电容(CAP)的透射电镜HAADF-STEM像及TEM-EDS分析结果。图3为图2中顶部电容的横截面结果。数据使用JED双100mm2EDS探头及牛津仪器 AZtecTEM软件进行采集。

之间的连接则利用溅射沉积Co然后退火得到CoSi2合金,形成欧姆接触并改善附着性。Ti与N,W与Si都是大规模集成电路中常用的元素,但他们之间存在严重谱峰重叠,如果不能准确识别,将会造成结果的误判,图2中Ti与N,W与Si的分布与DRAM的设计一致,证明数据的采集及处理无误。

图3中的EDS结果可判断该DRAM的电容由外至内为TiN-Al2O3-ZrO2-TiN-ZrO2-Al2O3-TiN,其中Al2O3从STEM像中无法区分。Al2O3层的厚度约2.6-2.7nm,TiN的厚度由3.5-6.5nm不等,ZrO2的厚度约5.5nm,均在10nm以下,但TEM-EDS可以清晰地将它们表征出来,丰富电子图像的信息。

图4为在SU9000上STEM模式下使用牛津仪器无窗能谱Extreme分析的另一DRAM电容结构。其中,TiN和ZrO2以及电容周围的SiGe均清晰可见,只有最薄的Al2O3介质层未能很好地表征出来,这说明现代的SEM-EDS已经可以非常好地表征5nm左右的结构。

3. 3D NAND Flash

与SRAM和DRAM不同, NAND Flash是一种非易失性存储器(non-volatile memory,NVM),是固态硬盘(Solid State Drive,SSD)中的存储器部分。与机械硬盘相比,NANA Flash可靠性高,读写速度更快,但成本及容量曾是其广泛应用的最大阻碍。2D NAND尺寸缩小到十几纳米节点,每个单元尺寸变的非常小,每个单元中电子的串扰问题使得尺寸继续微缩变得愈加困难且不够经济,因此出现了3D NAND,它将内存颗粒堆叠在一起来解决2D或者平面NAND闪存带来的限制。随着堆叠层数的增加,3D NAND工艺会对高纵深比的蚀刻及沉积工艺提出更高的要求,各种显微分析手段也会越来越多地被应用于良率控制、失效分析及新品研发中。

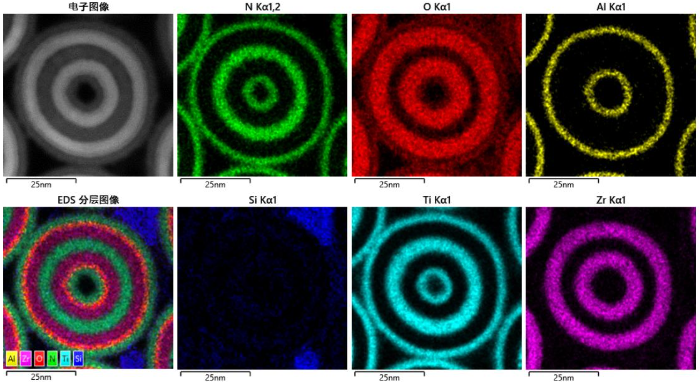

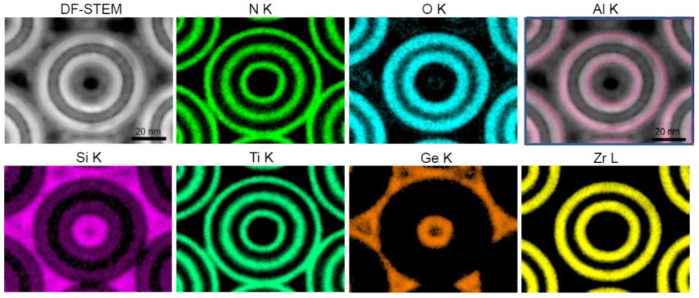

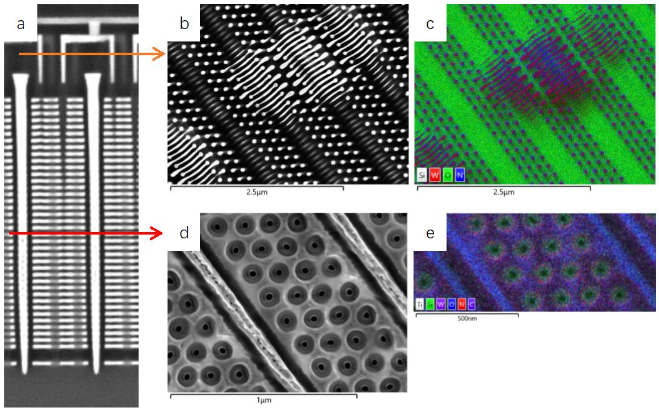

图5所示为一个32L 3D V-NAND的EDS分析结果。图5(a)显示的是BL方向的V-NAND横截面扫描电镜电子图像,使用离子束研磨到黄线所示的Bitline straps处,在3kV下俯视该结构,电子图像和元素分布如图5(b)、5(c)所示;继续使用离子束研磨至WL(Control Gate),其俯视电子图及3kV下的元素分布如图5(d)、5(e)所示。元素分布均可与结构一一对应,轻元素N、O分布清晰可见,且Si与W区分准确。图d中的存储单元(图中圆孔)结构十分复杂,在TEM下观察为多个环形分层,由内至外的结构为SiOx-Poly Si-ONO组成,每一层都需要用CVD,ALD或者EPI工艺来沉积,因此SEM低电压不足以表征存储单元内的精细结构,可以选择扫描电镜中的STEM模式或者透射电镜进行观察。

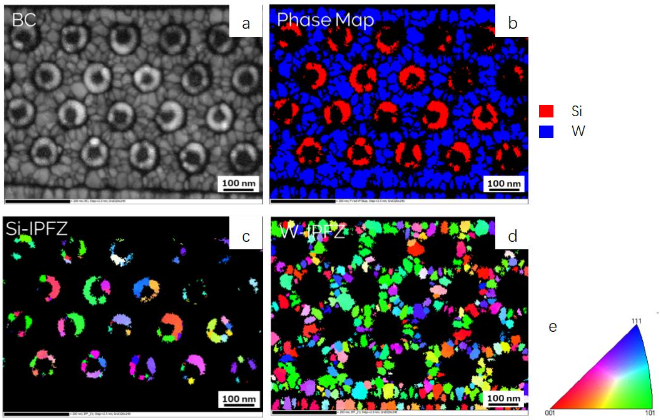

WL和存储单元的结晶性及晶粒尺寸和取向都有可能影响闪存的读写速度和可靠性等。在EDS分析的基础上,可以利用TKD技术对WL和存储单元中的多晶硅进行晶体学分析。

图6所示为NAND String的EBSD结果,数据使用SU7000及牛津仪器Symmetry EBSD进行采集,采集电压为20kV。图a和b显示的分别是带对比度和相分布图,相分布图的结果显示WL部分为W,电荷存储单元材料为Si。图c中W结晶完整,晶粒为等轴晶,晶粒尺

寸约为20nm,晶粒似有<101>//纸面法线方向的趋势,但因为扫描区域较小,不能得出确定的结论,如需要类似晶粒取向的分布,则需要选择不同的区域综合分析。图d中Si为多晶硅,这也与制成中的poly gate相符,部分多晶Si未能标定,最可能的原因是晶粒尺寸过

小。W与Si之间有明显界限,这是因为ONO层及SiO层均为非晶,多晶硅中心的SiO层亦是因为相同原因没有标定。

利用EBSD可以对IC中的晶体(通常为导电部分)进行微区分析,得到诸如相鉴定、晶粒尺寸分析、取向分析、界面分析、应力分析等微观的可视化结果,其分辨率和分析区域介于XRD与TEM之间,可以提供十纳米至厘米级的分析结果,为IC失效分析和材料设计提供更全面的晶体学信息。

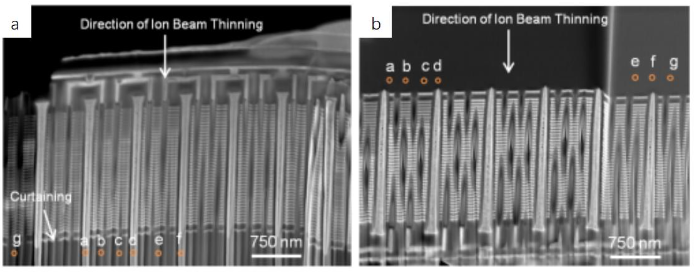

上述案例中的样品是利用双束电镜(FIB)制备的,IC中大多数TEM样品都需要通过FIB来制备,离子束用于挖坑及减薄样品,提取样品及点焊则需要纳米操作手OmniProbe协助完成。IC样品尺度小,结构复杂,为了避免提取样品过程中不引入应力改变样品状态甚至损毁样品,要求纳米操作手具有足够好的编码步进精度。此外,类似3D NAND这种深纵宽比的样品,如果使用传统的截面制备方法,在样品的下端将会出现诸如窗帘效应、再沉积、难以减薄等问题,如果分析区域正好位于样品下端(如PCGs,Pipe Control Gates)时则最终减薄效果不佳,此类样品可以选择背切的方式获得更好的实验结果。

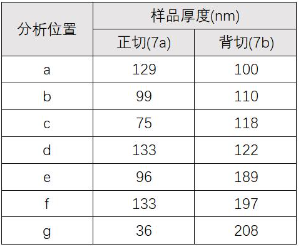

图7所示为一个需要重点观察下端晶体管部分的3D NAND样品利用传统截面制备方法和背切制备后样品形貌。图a中的样品是从上端的位线往下减薄的,Source Line Contact底端及PCGs处出现了严重的窗帘效应;图b所示为背切的样品,减薄时离子束从NAND下端的PCGs往位线切,重点观察区域平整。在a图b图中分别标出了a-g几个点的位置,利用牛津仪器厚度测量软件Layerprobe在这些点上进行厚度测量,测量结果如表1所示。对比可发现,相较于传统正切的样品,背切样品在观察区域的厚度更为均匀(背切样品e-g点厚度与a-d点不同是因该部分未做最终减薄处理,见图7b)。

背切样品的制备工序相较于正切样品更为复杂,如果使用具有原位旋转功能的纳米操作手OP350或OP400进行,配合可调节倾转角的TEM样品槽底座,则只需取出样品一次就可以制备背切样品,这样就大大缩短了背切样品的制备时间,显著提高工作效率。

样品结构复杂、尺寸微缩是半导体样品的共同特点。在EDS分析过程时,可以通过降低电压来提高块体分辨率或增加轻元素检测率,也可以通过制备薄片样品使用STEM模式来提高分辨率,但无论是哪种方式,都需要增加有效信号才能得清晰的元素分布结果,牛津仪器在扫描电镜SEM上和双束电镜FIB上提供了不同晶体面积的有窗能谱UltimMax系列及Ultim Extreme无窗能谱以表征不同尺寸及元素的结构。除了空间分辨率,半导体样品在能谱EDS分析时通常需要区分重叠峰元素,如Si和W,Cu和Hf、Ta,N和Ti等,这些元素不能通过增加EDS信号来区分,只能通过准确收集每个元素的EDS信号并经数据库中每个元素的实测峰形峰位进行拟合后做去卷积处理方能区分,牛津仪器的AZtecEDS软件包中的数据库和算法可以轻松区分半导体样品中常见的重叠峰元素,如Si和W,Cu和Hf、Ta等,并实现一键还原真实元素分布功能(Trumap及Truline),避免了因操作不同而出现不同结果的现象,保证了结果的一致性及准确性。空间分辨率及灵敏性是IC样品EBSD分析的难点,牛津仪器推出的Symmetry EBSD探测系统采用CMOS耦合光纤技术,兼顾了高速和高灵敏度的特点,再结合透射EBSD(TKD)技术可以大大提高在SEM或FIB中表征IC样品的可能性。 更多牛津仪器探测器的信息,详见牛津仪器纳米分析部官网https://nano.oxinst.cn/

参考文献:

[1] https://zhuanlan.zhihu.com/p/3...

[2] https://www.icinsights.com/ser...

[3] https://www.dzsc.com/data/2013...

点击咨询更多 公安机关备案号31010402003473

公安机关备案号31010402003473